- Инјю

/ЦРОД/

/ЦРОД/

/ЦРОД/

/ЦРОД/

/ЦРОД/

/ЦРОД/

/ЦРОД/

/ЦРОД/

/ЦРОД/

/ЦРОД/

QQУОП·ҙуМь2022№Щ·ҪПВФШХэКҪ°жv5.41.57773.0 ЧоРВ°ж

QQУОП·ҙуМь2022№Щ·ҪПВФШХэКҪ°жv5.41.57773.0 ЧоРВ°ж МЪС¶QQПВФШv9.5.9 ЧоРВ°ж

МЪС¶QQПВФШv9.5.9 ЧоРВ°ж QQөзДФ№ЬјТv15.0.22206.230 ЧоРВХэКҪ°ж

QQөзДФ№ЬјТv15.0.22206.230 ЧоРВХэКҪ°ж АЧЙсДЈДвЖчҫ«јт№ӨҫЯv1.0 ВМЙ«°ж

АЧЙсДЈДвЖчҫ«јт№ӨҫЯv1.0 ВМЙ«°ж ЖуТөОўРЕөзДФ°жv4.0.6.6516 №Щ·ҪPC°ж

ЖуТөОўРЕөзДФ°жv4.0.6.6516 №Щ·ҪPC°ж ГАНјРгРгөзДФ°жv6.5.5.0 №Щ·Ҫ°ж

ГАНјРгРгөзДФ°жv6.5.5.0 №Щ·Ҫ°ж 360УОП·ҙуМьөзДФ°жv6.0.0.1052 ЧоРВ°ж

360УОП·ҙуМьөзДФ°жv6.0.0.1052 ЧоРВ°ж СёАЧ11v11.3.9.1902 №Щ·Ҫ°ж

СёАЧ11v11.3.9.1902 №Щ·Ҫ°ж Гў№ыTVҝН»§¶Лv6.5.5.0 №Щ·Ҫ°ж

Гў№ыTVҝН»§¶Лv6.5.5.0 №Щ·Ҫ°ж НшТЧФЖТфАЦpcҝН»§¶Лv2.9.8 №Щ·Ҫ°ж

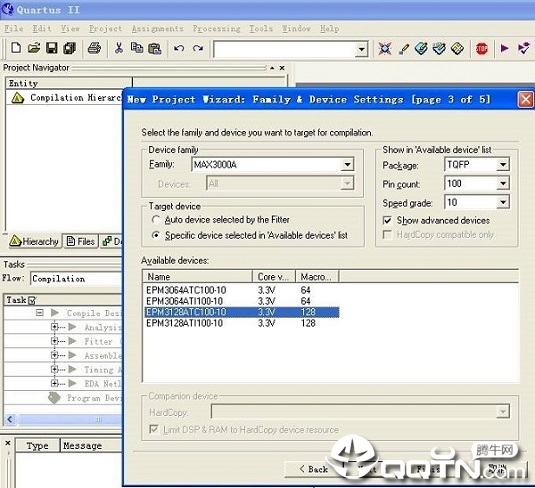

НшТЧФЖТфАЦpcҝН»§¶Лv2.9.8 №Щ·Ҫ°жQuartus II КЗAltera№«ЛҫөДЧЫәПРФPLD/FPGAҝӘ·ўИнјюЈ¬Ц§іЦФӯАнНјЎўVHDLЎўVerilogHDLТФј°AHDLөИ¶аЦЦЙијЖКдИлРОКҪЈ¬ДЪЗ¶ЧФУРөДЧЫәПЖчТФј°·ВХжЖчЈ¬ҝЙТФНкіЙҙУЙијЖКдИлөҪУІјюЕдЦГөДНкХыPLDЙијЖБчіМЎЈ

¶ФУЪFPGAЎўCPLDТФј°Ҫб№№»ҜASICЙијЖЈ¬quartus ii 11.0КЗРФДЬәНР§ДЬКЧЗьТ»ЦёөДЙијЖИнјюЎЈИнјюЦ§іЦAlteraГыОӘQsysөДПөНіј¶јҜіЙ№ӨҫЯРВІъЖ·Ј¬КөПЦБЛ¶ФStratix® V FPGAПөБРөДА©Х№Ц§іЦЈ¬ІўЗТІЙУГФцЗҝәуөДөчКФ·Ҫ°ёјУҝмБЛөзВ·°еҝӘ·ўЎЈХвКЗМṩПВФШөДКЗquartus ii 11.0ЖЖҪвЈ¬УРРиТӘөДЕуУСҝЙГв·СПВФШ!

1ЎўQuartus IIЙијЖИнјюТІҝЙТФЧФ¶ҜөШҙУQuartusII·ВХжЖчІЁРООДјюЦРҙҙҪЁНкХыөДHDLІвКФЖҪМЁ

2ЎўЦ§іЦёЯЛЩI/OЙијЖЈ¬ЙъіЙЧЁУГI/O»әіеРЕПў№ж·¶ЈЁIBISЈ©ДЈРНөјИлөҪіЈУГөДEDAРЕәЕјҜіЙ№ӨҫЯЦРЎЈIBISДЈРНёщҫЭЙијЖЦРГҝёц№ЬҪЕөДI/OұкЧјЙиЦГАҙ¶ЁЦЖЈ¬јт»ҜөЪИэ·Ҫ№ӨҫЯөД·ЦОц

3ЎўЦ§іЦЛ«әЛCPUөДЗ¶Ил

4ЎўҝЙАыУГФӯАнНјЎўҪб№№ҝтНјЎўVerilogHDLЎўAHDLәНVHDLНкіЙөзВ·ГиКцЈ¬ІўҪ«ЖдұЈҙжОӘЙијЖКөМеОДјюЈ»

РҫЖ¬ЈЁөзВ·Ј©ЖҪГжІјҫЦБ¬ПЯұајӯ

5ЎўLogicLockФцБҝЙијЖ·Ҫ·ЁЈ¬УГ»§ҝЙҪЁБўІўУЕ»ҜПөНіЈ¬И»әуМнјУ¶ФФӯКјПөНіөДРФДЬУ°ПмҪПРЎ»тОЮУ°ПмөДәуРшДЈҝй

№ҰДЬЗҝҙуөДВЯјӯЧЫәП№ӨҫЯ

6ЎўНкұёөДөзВ·№ҰДЬ·ВХжУлКұРтВЯјӯ·ВХж№ӨҫЯ

7Ўў¶ЁКұ/КұРт·ЦОцУл№ШјьВ·ҫ¶СУКұ·ЦОц

8ЎўҝЙК№УГSignalTap IIВЯјӯ·ЦОц№ӨҫЯҪшРРЗ¶ИлКҪөДВЯјӯ·ЦОц

9ЎўЦ§іЦИнјюФҙОДјюөДМнјУәНҙҙҪЁЈ¬ІўҪ«ЛьГЗБҙҪУЖрАҙЙъіЙұаіМОДјю

10ЎўК№УГЧйәПұаТл·ҪКҪҝЙТ»ҙОНкіЙХыМеЙијЖБчіМ

11ЎўЧФ¶Ҝ¶ЁО»ұаТлҙнОу

12ЎўёЯР§өДЖЪјдұаіМУлСйЦӨ№ӨҫЯ

13ЎўҝЙ¶БИлұкЧјөДEDIFНшұнОДјюЎўVHDLНшұнОДјюәНVerilogНшұнОДјю

14ЎўДЬЙъіЙөЪИэ·ҪEDAИнјюК№УГөДVHDLНшұнОДјюәНVerilogНшұнОДјю

Т»ЎўQuartusIIЦРөДУЕ»ҜЙиЦГ

Т»°г¶ј»бФЪassignment/settingsЦРҪшРРЙиЦГ

1.И«ҫЦУЕ»Ҝ

ФЪassignment/settings/Ј¬physical synthesis optimizationЦРЈ¬УРјёёцСЎПо:

(1)optimize for performance(РФДЬУЕ»Ҝ)

perform physical synthesis for combinational logic ¶ФЧйәПВЯјӯҪшРРУЕ»Ҝ

perform register retiming ¶ФјДҙжЖчҪшРРУЕ»Ҝ

(2)effort level ј¶ұр

ПаУҰөДІ»Н¬өДј¶ұрөДІ»Н¬Ц®ҙҰФЪәуГжөДҪвКНЦРЛөГч,ЦчТӘМеПЦФЪБЛұаТлКұјдөД¶аЙЩ,өұИ»УлМбёЯөДРФДЬЦ®јдіК·ҙұИөД№ШПө

(3)fitter netlist optimization ІјҫЦІјПЯНшұнУЕ»Ҝ

өЪТ»ёцСЎПоКЗ¶ФТмІҪРЕәЕЧФ¶ҜөДМнјУБчЛ®ПЯ

өЪ¶юёцСЎПоЦҙРРјДҙжЖчөДёҙУГ

(4)optimize for fitting ІјҫЦІјПЯөДУЕ»Ҝ

өЪТ»ёцСЎПоКЗХл¶ФЧйәПВЯјӯөзВ·¶шСФ

өЪ¶юёцСЎПо ¶ФВЯјӯәНјДҙжЖчҪшРРУЕ»Ҝ

2.ЧЫәПУЕ»Ҝ

ФЪУЕ»ҜјјЗЙ(optimization technique)ЦРУРИэЦЦСЎФс:јҙЈә ЛЩ¶ИУЕПИ,ЖҪәвУЕПИ,Гж»эУЕПИ,»№УРpowerplay power optimizationјҙ№ҰВКУЕ»Ҝ

ИфСЎФсextra effortЈ¬ЧЫәПЖчҪ«ҪшРР№ҰВКУЕ»Ҝ,ө«ҝЙДЬ»бҪөөНХыёцЙијЖөДРФДЬ

3.ККЕдУЕ»Ҝ

°ьАЁұЈіЦКұРтУЕ»Ҝ ¶а№ХҪЗКұРтУЕ»Ҝ

ұЈіЦКұРтУЕ»ҜФКРнККЕдЖчНЁ№эФЪәПККөДВ·ҫ¶ЦРМнјУСУіЩ,ҙУ¶шКөПЦұЈіЦКұРтөДУЕ»Ҝ,№ШұХёГСЎПо,ФтІ»»б¶ФИОәОВ·ҫ¶ҪшРРУЕ»Ҝ

¶а№ХҪЗКұРтУЕ»ҜУГУЪҝШЦЖККЕдЖчКЗ·с¶ФЙијЖҪшРРУЕ»ҜТФВъЧгЛщУР№ХҪЗөДКұРтТӘЗуәНІЩЧчМхјюЎЈТӘК№УГХвПо№ҰДЬ,ұШРлК№ДЬКұРтВЯјӯУЕ»Ҝ

Т»ЎўМЧјю

УГ»§ТӘПлНкХыөДК№УГ Ј¬РиТӘ°ІЧ°ПаУҰөДМЧјюЈ¬РиПВФШөДМЧјю:

1.Quartus II 9.1Ц®З°өДИнјюЧФҙш·ВХжЧйјюЈ¬¶шЦ®әуИнјюІ»ФЩ°ьә¬ҙЛЧйјюЈ¬ТтҙЛұШРлТӘ·ВХж°ІЧ°Modelsim

2.Quartus II 9.1Ц®З°өДИнјюЧФҙшУІјюҝвЈ¬І»РиТӘ¶оНвПВФШ°ІЧ°Ј¬¶ш10.0ҝӘКјРиТӘ¶оНвПВФШУІјюҝвЈ¬БнРРСЎФс°ІЧ°

3.Quartus II 11.0Ц®З°өДИнјюРиТӘ¶оНвПВФШNios II ЧйјюИфРиТӘЙППөНіЈ¬¶ш11.0ҝӘКјQuartus II ИнјюЧФҙшNios IIЧйјю

4.Quartus II 9.1Ц®З°өДИнјюЧФҙшSOPCЧйјюЈ¬¶шQuartus 10.0ЧФҙшSOPCТСҫӯQsysБҪёцЧйјюЈ¬ө«ҙУ10.1ҝӘКјЈ¬Quartus IIЦ®°ьә¬QsysЧйјю

5.Quartus II 10.1Ц®З°Инјю°ьАЁКұЦУЧЫәПЖчЈ¬јҙSettingsЦР°ьә¬TimeQuest Timing AnalyzerЈ¬ТФј°Classic Timing AnalyzerЈ¬ө«10.1ТФәуөД°жұҫЦ»°ьә¬БЛTimeQuset Time AnalyzerЈ¬ТтҙЛРиТӘsdcАҙФјКшКұРт

¶юЎўЧйјю

1.11.0_quartus_windows.exe :Quartus II Инјю

2.11.0_devices_windows.exe :Quartus II УІјюҝв

3. 11.0_modelsim_ase_windows.exe :Altera Modelsim ·ВХжИнјю

1ЎўҫЯМеОКМв

°ІЧ°quartus ii 11.0ИнјюәуЈ¬ҫӯ№эЖЖҪвЖчЙъіЙlicense.datОДјюәуЈ¬КөјКҪЁБў№ӨіМәуЈ¬ұаТлЧЫәП№ӨіМөДКұәт»біцПЦlicense.datОДјюУлРҫЖ¬І»ЖҘЕдөДОКМв

2ЎўПёҪЪГиКц

Warning: FLEXlm software error: Invalid (inconsistent) license key. The license key and data for the feature do not match. This usually happens when a license file has been altered. Feature: quartus License path: C:\altera\license.dat; FLEXnet Licensing error:-8,523 For further information, refer to the FLEXnet Licensing documentation, available at www.acresso.com

Error: Current license file does not support the EP2C8Q208C8 device

3ЎўҪвҫц·Ҫ°ё

ФЪФЛРРЖЖҪвЖчЙъіЙlicense.datОДјюәуЈ¬УГјЗКВұҫёсКҪҙтҝӘlicense.datОДјюЈ¬Ҫ«АпГжhost IDәуГжөДXXXXXXXXXXXXёДіЙДгөзДФөДНшҝЁәЕЈ¬ЧўТвlicense.datОДјюЦРҙжФЪБҪёцhost IDәЕЎЈЖдКөҙтҝӘТС°ІЧ°әГөД

quartus ii 11.0ИнјюәуЈ¬СЎФсtools->License Setupҙ°ҝЪЈ¬ҝЙТФХТөҪБҪёцNIC IDәЕЈ¬ёХәГ°ҙПИәуЛіРтМоРҙИлlicense.datОДјюЦРөДБҪёцhost IDЈ¬ҫНҝЙТФБЛ

өзВ·Нј»жЦЖИнјюЈ¬өзВ·НјЙијЖИнјюПВФШЎЈөзВ·Нј»жЦЖИнјюКЗЧЁГЕУГАҙ»жЦЖөзЖшөзВ·НјөД№ӨҫЯЈ¬ҝЙТФ°пЦъЙијЖИЛФұҝмЛЩ»жЦЖёчЦЦёҙФУөДөзВ·НјЈ¬ҪЪКЎКұјдЈ¬МбёЯР§ТжЎЈДҝЗ°НшЙПөДөзВ·Нј»жЦЖИнјюЦЦАа¶аСщЈ¬ДЗГҙДДҝоәГУГДШЈҝТФПВКЗ

өзВ·Нј»жЦЖИнјюУРДДР©Ј¬өзВ·Нј»жЦЖИнјюПВФШЎЈөзВ·ЙијЖИнјюҫНКЗөзВ·Нј»жЦЖЎўУЕ»ҜЎўІвКФЎў·ВХжАаИнјюЎЈДЗГҙіЈУГөДөзВ·ЙијЖИнјюУРДДР©ДШЈҝФЪ№ъДЪЈ¬ҝӘ·ўК№УГ¶аөДИнјюИзПВЈәprotelЈ¬powerpcbЈ¬AllegroЈ¬orcadЈ¬cam350өИөИ

Altium Designer2021ЦРОДЖЖҪв°ж(ЧЁТөPCB°еЙијЖ)v21.2.1.34 Гв·С°ж»ъРөөзЧУ / 2.54G

Altium Designer2021ЦРОДЖЖҪв°ж(ЧЁТөPCB°еЙијЖ)v21.2.1.34 Гв·С°ж»ъРөөзЧУ / 2.54G

LedshowTWv2017 №Щ·Ҫ°ж»ъРөөзЧУ / 277.2M

LedshowTWv2017 №Щ·Ҫ°ж»ъРөөзЧУ / 277.2M

өз№Ө·ВХжҪМС§ИнјюВМЙ«ЦРОД°жV2019 Гв·С°ж»ъРөөзЧУ / 7.4M

өз№Ө·ВХжҪМС§ИнјюВМЙ«ЦРОД°жV2019 Гв·С°ж»ъРөөзЧУ / 7.4M

machiningКэҝШ·ВХжИнјюЖЖҪв°жv2.1.1.8 ЦРОД°ж»ъРөөзЧУ / 9.7M

machiningКэҝШ·ВХжИнјюЖЖҪв°жv2.1.1.8 ЦРОД°ж»ъРөөзЧУ / 9.7M

ANSYS Products2021v21.1.0.2020110819 ЖЖҪв°ж»ъРөөзЧУ / 17.70G

ANSYS Products2021v21.1.0.2020110819 ЖЖҪв°ж»ъРөөзЧУ / 17.70G

Polar Instruments(PCBЧиҝ№јЖЛгЖч)v11.0.4 ЦРОД°ж»ъРөөзЧУ / 18.8M

Polar Instruments(PCBЧиҝ№јЖЛгЖч)v11.0.4 ЦРОД°ж»ъРөөзЧУ / 18.8M

Altium Designer 2020ЖЖҪв°жv20.0.2 ЧоРВ°ж»ъРөөзЧУ / 3.41G

Altium Designer 2020ЖЖҪв°жv20.0.2 ЧоРВ°ж»ъРөөзЧУ / 3.41G

ұҫМпHDSХп¶ПИнјюv3.102.004 Гв·С°ж»ъРөөзЧУ / 97.2M

ұҫМпHDSХп¶ПИнјюv3.102.004 Гв·С°ж»ъРөөзЧУ / 97.2M

commproxyЈЁНЁС¶ЧӘ·ўЈ©v1.1 Гв·С°ж»ъРөөзЧУ / 338KB

commproxyЈЁНЁС¶ЧӘ·ўЈ©v1.1 Гв·С°ж»ъРөөзЧУ / 338KB

Altium Designer(PCBЙијЖИнјю)v17.1.9.592 ЦРОД°ж»ъРөөзЧУ / 3.61G

Altium Designer(PCBЙијЖИнјю)v17.1.9.592 ЦРОД°ж»ъРөөзЧУ / 3.61G

Polar Instruments(PCBЧиҝ№јЖЛгЖч)v11.0.4 ЦРОД°ж»ъРөөзЧУ / 18.8M

Polar Instruments(PCBЧиҝ№јЖЛгЖч)v11.0.4 ЦРОД°ж»ъРөөзЧУ / 18.8M

ANSYS Products2021v21.1.0.2020110819 ЖЖҪв°ж»ъРөөзЧУ / 17.70G

ANSYS Products2021v21.1.0.2020110819 ЖЖҪв°ж»ъРөөзЧУ / 17.70G

өз№Ө·ВХжҪМС§ИнјюВМЙ«ЦРОД°жV2019 Гв·С°ж»ъРөөзЧУ / 7.4M

өз№Ө·ВХжҪМС§ИнјюВМЙ«ЦРОД°жV2019 Гв·С°ж»ъРөөзЧУ / 7.4M

Altium Designer 2020ЖЖҪв°жv20.0.2 ЧоРВ°ж»ъРөөзЧУ / 3.41G

Altium Designer 2020ЖЖҪв°жv20.0.2 ЧоРВ°ж»ъРөөзЧУ / 3.41G

SMPSKITөзФҙЙијЖјЖЛг№ӨҫЯv9.7 №Щ·Ҫ°ж»ъРөөзЧУ / 9.6M

SMPSKITөзФҙЙијЖјЖЛг№ӨҫЯv9.7 №Щ·Ҫ°ж»ъРөөзЧУ / 9.6M

proteus8.6әә»ҜМШұр°жёҪК№УГҪМіМv8.6 sp2ЖЖҪв°ж»ъРөөзЧУ / 250.0M

proteus8.6әә»ҜМШұр°жёҪК№УГҪМіМv8.6 sp2ЖЖҪв°ж»ъРөөзЧУ / 250.0M

Altium Designer2021ЦРОДЖЖҪв°ж(ЧЁТөPCB°еЙијЖ)v21.2.1.34 Гв·С°ж»ъРөөзЧУ / 2.54G

Altium Designer2021ЦРОДЖЖҪв°ж(ЧЁТөPCB°еЙијЖ)v21.2.1.34 Гв·С°ж»ъРөөзЧУ / 2.54G

CADe_SIMU(ДЈДвөзЖшөзВ··ВХжИнјю)v3.0 Гв·С°ж»ъРөөзЧУ / 8.6M

CADe_SIMU(ДЈДвөзЖшөзВ··ВХжИнјю)v3.0 Гв·С°ж»ъРөөзЧУ / 8.6M

machiningКэҝШ·ВХжИнјюЖЖҪв°жv2.1.1.8 ЦРОД°ж»ъРөөзЧУ / 9.7M

machiningКэҝШ·ВХжИнјюЖЖҪв°жv2.1.1.8 ЦРОД°ж»ъРөөзЧУ / 9.7M

Кў·ўөзЧУИхөз№ӨіМёЕФӨЛгИнјюv2018 Гв·С°ж»ъРөөзЧУ / 27.8M

Кў·ўөзЧУИхөз№ӨіМёЕФӨЛгИнјюv2018 Гв·С°ж»ъРөөзЧУ / 27.8M

әкҙпјЖјю№ӨЧК№ЬАнПөНіv3.0 №Щ·Ҫ°жІЖОс№ЬАн

әкҙпјЖјю№ӨЧК№ЬАнПөНіv3.0 №Щ·Ҫ°жІЖОс№ЬАн ҙъБ·НЁөзДФ°жv19.1.25.1 №Щ·Ҫ°жЖдЛыРРТө

ҙъБ·НЁөзДФ°жv19.1.25.1 №Щ·Ҫ°жЖдЛыРРТө ЛҰКЦ№ӨҫЯПдv5.07 Гв·С°жЙМТөГіТЧ

ЛҰКЦ№ӨҫЯПдv5.07 Гв·С°жЙМТөГіТЧ »ӘМ©ЦӨИҜНшЙПҪ»ТЧ·ЦОцПөНіЧЁТө°ж2v5.53 №Щ·ҪГв·С°ж№ЙЖұЦӨИҜ

»ӘМ©ЦӨИҜНшЙПҪ»ТЧ·ЦОцПөНіЧЁТө°ж2v5.53 №Щ·ҪГв·С°ж№ЙЖұЦӨИҜ »ў·еИЛКВ№ЬАнПөНіv5.0 №Щ·Ҫ°жРРХю№ЬАн

»ў·еИЛКВ№ЬАнПөНіv5.0 №Щ·Ҫ°жРРХю№ЬАн ХРЖёЦ®РЗv4.5.6.5 №Щ·Ҫ°жРРХю№ЬАн

ХРЖёЦ®РЗv4.5.6.5 №Щ·Ҫ°жРРХю№ЬАн Т»јь№ӨЧчКТ(Т»јьuЕМЧ°ПөНі)V4.2UEFI°жЖдЛыРРТө

Т»јь№ӨЧчКТ(Т»јьuЕМЧ°ПөНі)V4.2UEFI°жЖдЛыРРТө AHИЛКВ№ЬАнПөНі3.85 Гв·С°жРРХю№ЬАн

AHИЛКВ№ЬАнПөНі3.85 Гв·С°жРРХю№ЬАн ҝЙЕЈЙұ¶ҫПөНіОДјюРЮёҙ№ӨҫЯ1.1 ВМЙ«°жЖдЛыРРТө

ҝЙЕЈЙұ¶ҫПөНіОДјюРЮёҙ№ӨҫЯ1.1 ВМЙ«°жЖдЛыРРТө

№ШУЪМЪЕЈ | БӘПө·ҪКҪ | ·ўХ№АъіМ | °жИЁЙщГч | ПВФШ°пЦъ(Јҝ) | №гёжБӘПө | НшХҫөШНј | УСЗйБҙҪУ

Copyright 2005-2022 QQTN.com ЎҫМЪЕЈНшЎҝ °жИЁЛщУР ¶хICPұё2022005668әЕ-1 |  ¶х№«Нш°Іұё 42011102000260әЕ

¶х№«Нш°Іұё 42011102000260әЕ

ЙщГчЈәұҫХҫ·ЗМЪС¶QQ№Щ·ҪНшХҫ ЛщУРИнјюәНОДХВАҙЧФ»ҘБӘНш ИзУРТмТй ЗлУлұҫХҫБӘПө ұҫХҫОӘ·ЗУ®АыРФНшХҫ І»ҪУКЬИОәОФЮЦъәН№гёж