- 软件

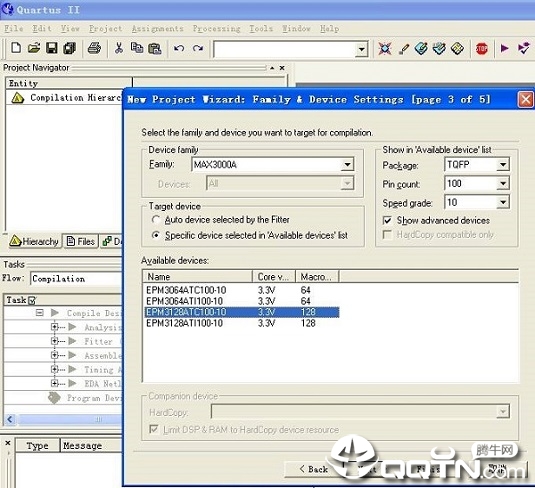

Quartus II是Altera公司于推出一款综合性PLD/FPGA开发软件,内置强大的综合器和仿真器,支持原理图、VHDL、VerilogHDL以及AHDL等多种设计文件的输入,可轻松完成从设计输入到硬件配置的整个PLD设计流程。欢迎下载体验。

对于FPGA、CPLD以及结构化ASIC设计,quartus ii 11.0是性能和效能首屈一指的设计软件。软件支持Altera名为Qsys的系统级集成工具新产品,实现了对Stratix® V FPGA系列的扩展支持,并且采用增强后的调试方案加快了电路板开发。

1.自动定位编译错误;

2.高效的期间编程与验证工具;

3.功能强大的逻辑综合工具;

4.芯片(电路)平面布局连线编辑;

5.定时/时序分析与关键路径延时分析;

6.完备的电路功能仿真与时序逻辑仿真工具;

7.使用组合编译方式可一次完成整体设计流程;

8.可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;

9.能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件;

10.支持软件源文件的添加和创建,并将它们链接起来生成编程文件。

1.Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。

2.Quartus II提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;芯片(电路)平面布局连线编辑等功能!

Quartus ii简介:

Quartus II 是Altera公司的综合性PLD/FPGA开发软件,原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware 支持Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程

Altium Designer2021中文破解版(专业PCB板设计)v21.2.1.34 免费版机械电子 / 2.54G

Altium Designer2021中文破解版(专业PCB板设计)v21.2.1.34 免费版机械电子 / 2.54G

LedshowTWv2017 官方版机械电子 / 277.2M

LedshowTWv2017 官方版机械电子 / 277.2M

电工仿真教学软件绿色中文版V2019 免费版机械电子 / 7.4M

电工仿真教学软件绿色中文版V2019 免费版机械电子 / 7.4M

machining数控仿真软件破解版v2.1.1.8 中文版机械电子 / 9.7M

machining数控仿真软件破解版v2.1.1.8 中文版机械电子 / 9.7M

ANSYS Products2021v21.1.0.2020110819 破解版机械电子 / 17.70G

ANSYS Products2021v21.1.0.2020110819 破解版机械电子 / 17.70G

Polar Instruments(PCB阻抗计算器)v11.0.4 中文版机械电子 / 18.8M

Polar Instruments(PCB阻抗计算器)v11.0.4 中文版机械电子 / 18.8M

Altium Designer 2020破解版v20.0.2 最新版机械电子 / 3.41G

Altium Designer 2020破解版v20.0.2 最新版机械电子 / 3.41G

本田HDS诊断软件v3.102.004 免费版机械电子 / 97.2M

本田HDS诊断软件v3.102.004 免费版机械电子 / 97.2M

commproxy(通讯转发)v1.1 免费版机械电子 / 338KB

commproxy(通讯转发)v1.1 免费版机械电子 / 338KB

Altium Designer(PCB设计软件)v17.1.9.592 中文版机械电子 / 3.61G

Altium Designer(PCB设计软件)v17.1.9.592 中文版机械电子 / 3.61G

Polar Instruments(PCB阻抗计算器)v11.0.4 中文版机械电子 / 18.8M

Polar Instruments(PCB阻抗计算器)v11.0.4 中文版机械电子 / 18.8M

ANSYS Products2021v21.1.0.2020110819 破解版机械电子 / 17.70G

ANSYS Products2021v21.1.0.2020110819 破解版机械电子 / 17.70G

电工仿真教学软件绿色中文版V2019 免费版机械电子 / 7.4M

电工仿真教学软件绿色中文版V2019 免费版机械电子 / 7.4M

Altium Designer 2020破解版v20.0.2 最新版机械电子 / 3.41G

Altium Designer 2020破解版v20.0.2 最新版机械电子 / 3.41G

SMPSKIT电源设计计算工具v9.7 官方版机械电子 / 9.6M

SMPSKIT电源设计计算工具v9.7 官方版机械电子 / 9.6M

proteus8.6汉化特别版附使用教程v8.6 sp2破解版机械电子 / 250.0M

proteus8.6汉化特别版附使用教程v8.6 sp2破解版机械电子 / 250.0M

Altium Designer2021中文破解版(专业PCB板设计)v21.2.1.34 免费版机械电子 / 2.54G

Altium Designer2021中文破解版(专业PCB板设计)v21.2.1.34 免费版机械电子 / 2.54G

CADe_SIMU(模拟电气电路仿真软件)v3.0 免费版机械电子 / 8.6M

CADe_SIMU(模拟电气电路仿真软件)v3.0 免费版机械电子 / 8.6M

machining数控仿真软件破解版v2.1.1.8 中文版机械电子 / 9.7M

machining数控仿真软件破解版v2.1.1.8 中文版机械电子 / 9.7M

盛发电子弱电工程概预算软件v2018 免费版机械电子 / 27.8M

盛发电子弱电工程概预算软件v2018 免费版机械电子 / 27.8M